# AN13116

## Entering STBY mode on a single-core RT1170

Rev. 0 — 02 February 2021 Application Note

#### 1 Introduction

The i.MX RT1170 crossover processor is setting speed records at 1 GHz. This ground-breaking family combines superior computing power and multiple media capabilities with more usability and real-time functionality. The dual-core i.MX RT1170 runs on the Arm® Cortex®-M7 core at 1 GHz and Arm Cortex-M4 at 400 MHz, while providing best-in-class security. The i.MX RT1170 MCU offers support over a wide temperature range and is qualified for consumer, industrial, and automotive markets.

The RT1170 series is divided into two parts: single-core and dual-core. For details on the dual-core part and the most common settings, see AN13104.

Contents

This application note outline steps to enter the STBY mode on a single core RT1170 and simulate a single-core state on RT1170 EVK.

NOTE

The steps to enter the STBY mode on a single core RT1170 and simulate a single-core state on RT1170 EVK are two different operations.

The hardware is MIMXRT1170 EVK RevC1 (referred as EVK) and the software is based on SDK 2.9.0 with IAR IDE. The SDK demo has different projects for single-core and dual-core. The SDK demo also supports flash target and ram target.

#### 2 Overview

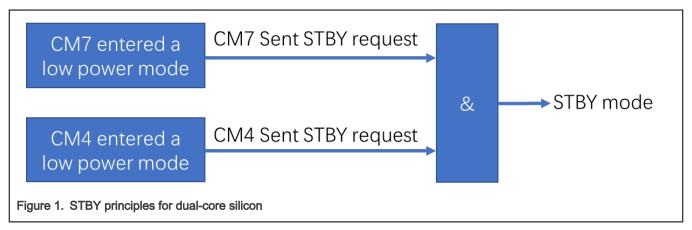

#unique\_3 shows that the basic principle of entering STBY is that both CPUs enter low-power mode and issue STBY requirements. The first principle is the CPU entering a low-power mode. The low-power mode here means CPU's status: . It can be WAIT, STOP, or SUSPEND mode. Each CPU can be in any state except run mode.

#### Such as:

- CM7 WAIT, CM4 STOP

- CM7 STOP, CM4 STOP

- · CM7 SUSPNED, CM4 WAIT

- CM7 SUSPEND, CM4 SUSPEND

The second principle is that both CPUs have sent the STBY request. If any CPU did not send it, the system cannot enter the STBY mode.

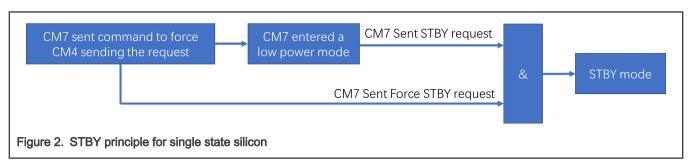

For single core silicon, CM4 cannot send this request signal. Therefore, some commands are a must to force the system enter the STBY mode.

For a single core silicon, the basic principle is CM7 enter a low-power mode and sent the stby\_request signal. The low-power mode here can be WAIT, STOP, or SUSPEND mode.

The basic flow is:

#### 3 Steps to enter the STBY mode on single-core RT1170

To enter the STBY mode, both the cores send the stby\_request. However, in a single-core silicon, such as RT1172 and RT1176, CM4 cannot send it. Therefore, the Force\_STBY function is used. The Force\_STBY function forces CM4 requesting the STBY mode. Once the M7 enters the low-power mode and sends an stby\_request, the whole chip enters the STBY mode.

GPC\_STBY\_CTRL->STBY\_MISC |= GPC\_STBY\_CTRL\_STBY\_MISC\_FORCE\_CPU1\_STBY\_MASK;

### 4 Steps to simulate single-core state on RT1170 EVK

EVK is based on RT1176 silicon, which is a dual-core silicon. Customer can simulate it as a single-core state after some settings.

NOTE

Simulation as a single-core state after some settings is only for early evaluation.

The basic method is CM4 entering suspend mode and sending the STBY request.

- 1. After system boot, CM7 configures some registers.

- 2. Write PGMC CM4 CPC register as CPU mode with power-off at SUSPEND.

- 3. Write GPC1 IRQ mask registers as 0xFFFFFFF so that no interrupt can wake it up.

- 4. Write GPC1 NON IRQ mask register as 0x3 to avoid a pending interrupt from debugger stop entering low-power mode.

- 5. Write GPC1 control register to request SUSPEND mode and SBTY mode.

- 6. CM7 releases CM4 by SRC\_SCR register. The silicon is now in the dual-core state.

- CM4 runs one instruction: assert WFI to trigger GPC1 low-power sequence to let itself from entering SUSPEND mode and send the STBY request.

- 8. When CM4 is in SUSPEND mode, CM7 writes some registers to lock CM4 by software.

- 9. Write GPC1 AUTHEN register to lock CM1 register access.

- 10. Write CM4 CCGR slice in CCM to gate off CM4 clock.

- 11. Write CM4 CCGR AUTHEN register 'allow\_list' and 'lock' fields meaning no CPU can access CM4 CCGR register. again. Thus CM7 software cannot turn on CM4 clock again.

- 12. Write PGMC CM4 CPC AUTHEN register to lock any access so that software cannot turn on CM4 power again.

The attachment of this application note is provided with detailed code for reference. The basic method is to let CM4 enter suspend mode and send STBY request. Based on this, mask all the wake-up sources in GPC CM1 and then lock the access rights of these registers: any CPU cannot access and modify. CM4 then enters the suspend mode and there is no wake-up source to wake it up and any CPU does not have the access right to change these settings.

The following API is able to complete above configuration.

void Powerdown\_CM4(void);

For details, see the attachment with this application note.

#### 5 Differences between a single-core silicon and simulated single-core on RT1176

There are some differences between a single-core silicon and a simulated single-core on RT1176. The first one is RDC. The single-core silicon cannot use RDC to assign a peripheral to a domain. If CM7 wants to access the RDC, a fault occurs. However, a simulated single-core on RT1176 can use RDC. For single-core silicon, all the peripherals are assigned to M7 domain. As a result, only 1 stop request from M7 domain is required during the handshake and only need to check the stop\_ack from M7 domain. For details on the handshake, see AN13104, Chapter 4.5.

Table 1. Differences between a single-core silicon and a simulated single-core on RT1176

|             | Single Core                                     | Simulated single core on RT1176 |

|-------------|-------------------------------------------------|---------------------------------|

| STBY Method | Force_STBY                                      | CM4 enters Suspend STBY         |

| RDC         | Not support                                     | Support                         |

| Handshake   | Only CM7 sends stop_req and checks the stop_ack | See AN13104, Chapter 4.5        |

# 6 Steps to create a single-core project on SDK

The MIMXRT1170 EVK supports single-core program executions. This section lists the steps to set up a single-core project by using different IDEs (IAR, Keil, and Arm GCC).

#### 6.1 Run a demo using IAR

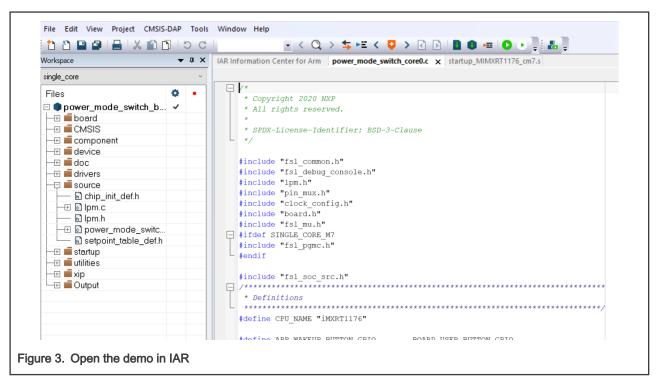

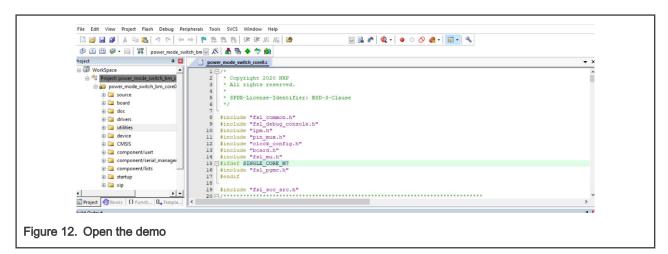

The following steps illustrate the power\_mode\_switch demo from SDK 2.9.0.

1. The location of the desired demo is:

```

<install_dir>\boards\evkmimxrt1170\demo_apps\power_mode_switch\bm\core0\iar\

power_mode_switch_bm_core0.eww

```

2. Import the demo into the IAR IDE.

Application Note 3/17

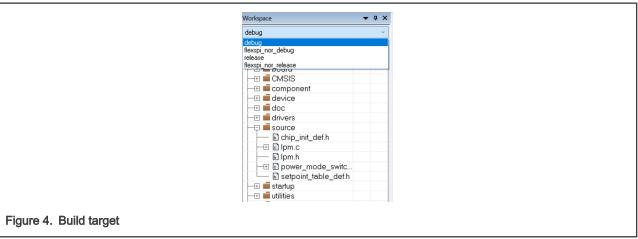

3. Debug the default build target as shown in Figure 4

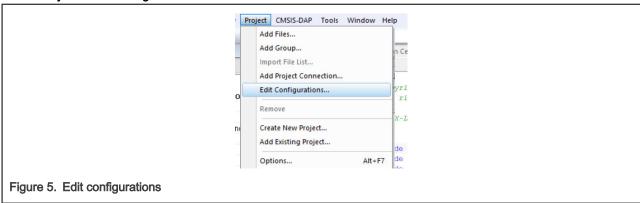

4. Select Project > Edit Configuration.

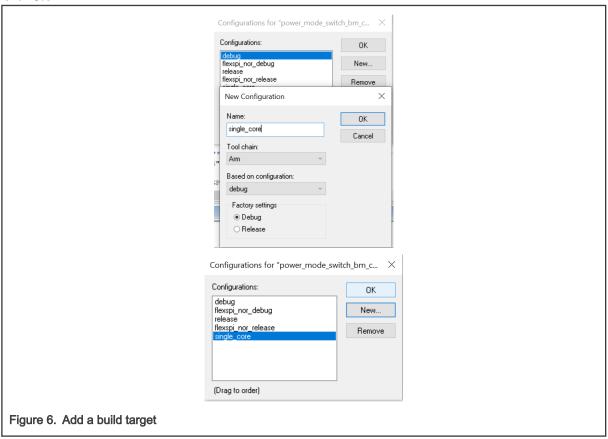

5. Add a build target.

- a. Click the New button.

- b. Name it as single\_core.

- c. Click OK.

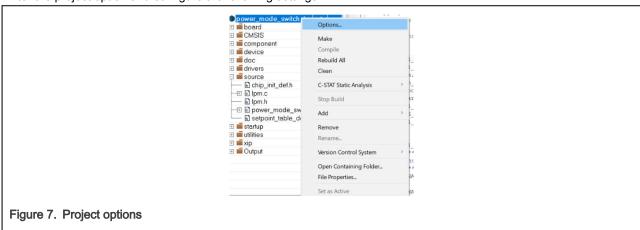

6. Enter the project option and configure the following settings.

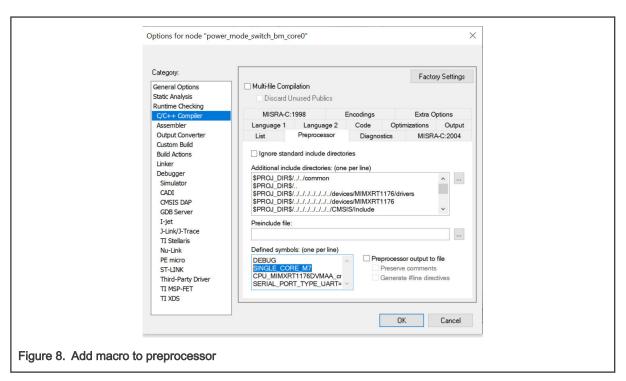

a. Add the macro 'SINGLE\_CORE\_M7' in the Preprocessor of C/C++ Compiler category.

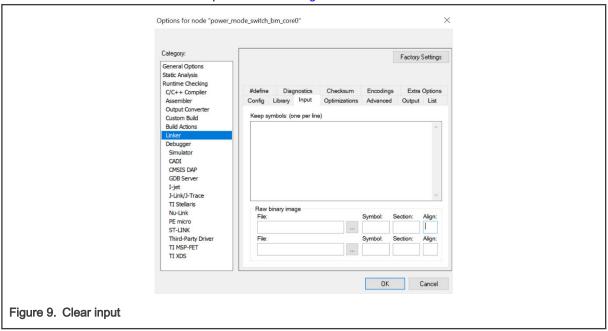

b. Delete all the information in the linker input as shown in Figure 9

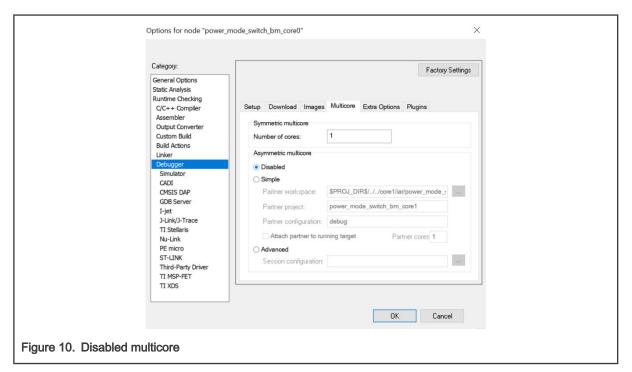

c. In the Debugger category, disable the multicore.

- 7. Debug and run the code.

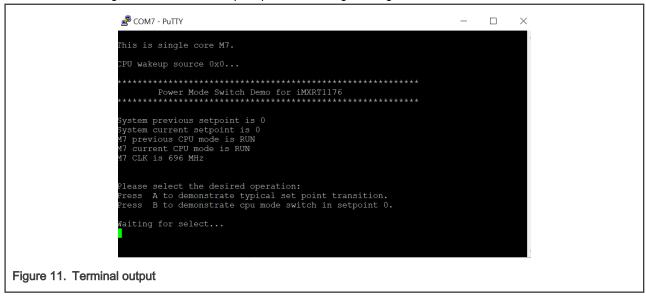

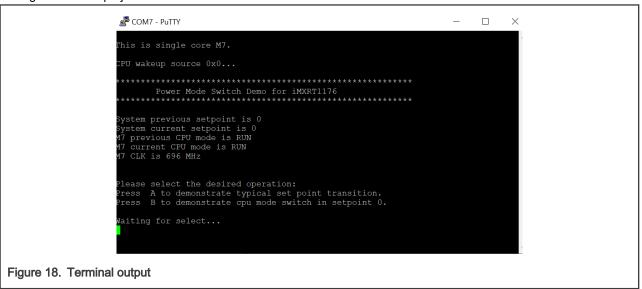

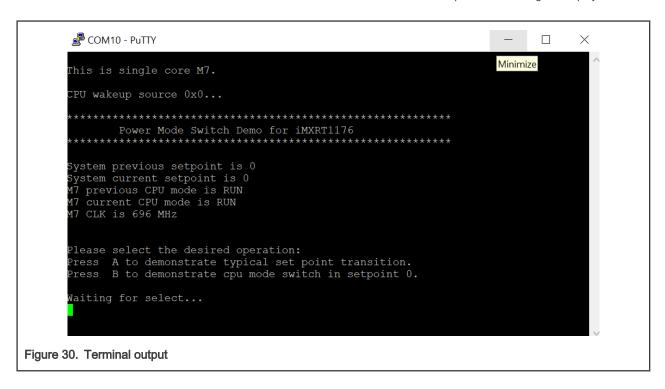

- 8. On successful debug, the terminal window prompts the following message.

# 6.2 Run a demo using Keil® MDK/µVision

1. Open the power\_mode\_switch project by using Keil. The project location is:

$\label{local_core0_mode_switch_bm_core0_mode_switch_bm_core0_mode_switch_bm_core0.uvmpw} $$ \cose0.uvmpw $$$

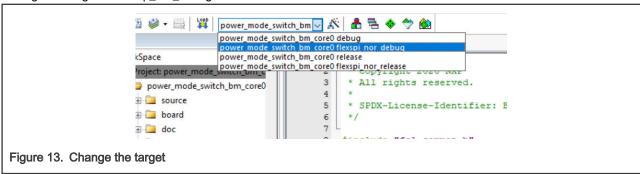

2. Change the target to flexsip\_nor\_debug.

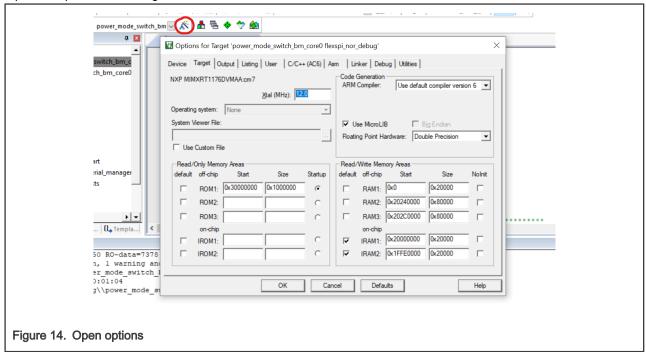

3. Open the options for the target.

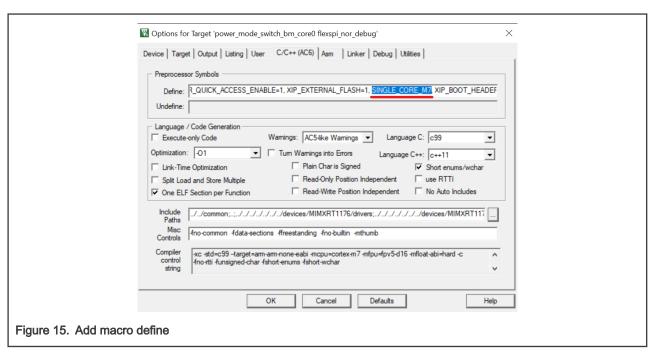

4. In C/C++ section, add 'SINGLE\_CORE\_M7' to the **Define** field.

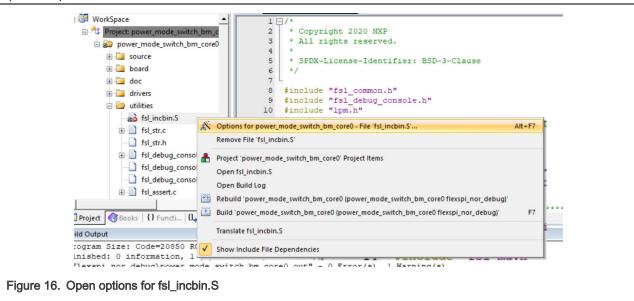

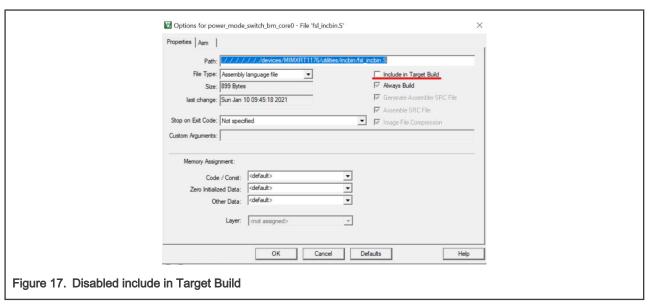

5. Open the options for the file fsl\_incbin.S under utilities.

6. Deselect the Include in Target Build checkbox.

7. Debug and run the project.

# 6.3 Run a demo using Arm® GCC

This section shows how to run a demo in a single-core mode by using GCC IDE.

**NOTE**Ensure that CMake and Segger J-Link are installed.

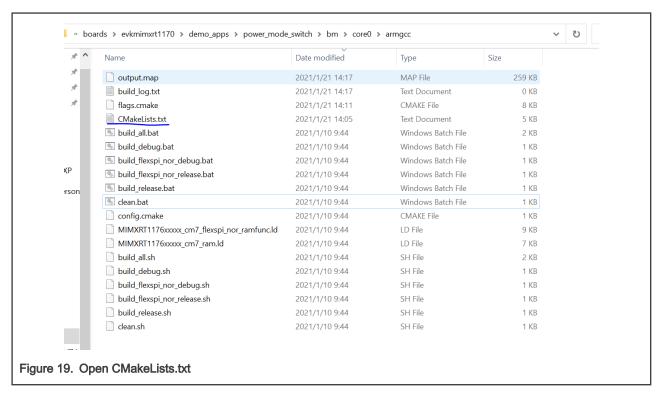

1. Open the cmakelist.txt in the project directory.

- 2. Delete or comments the following three parts of the code need.

- a. The code that include core1.

```

target_include_directories(${MCUX_SDK_PROJECT_NAME}) PRIVATE

${ProjDirPath}/../../common}

${ProjDirPath}/...}

# if((CMAKE_BUILD_TYPE_STREQUAL_debug) OR (CMAKE_BUILD_TYPE_STREQUAL_flexspi_nor_debug))

# target_include_directories(${MCUX_SDK_PROJECT_NAME}) PRIVATE ${ProjDirPath}/.../../corel/armgcc/debug)

# endif()

# if((CMAKE_BUILD_TYPE_STREQUAL_release) OR (CMAKE_BUILD_TYPE_STREQUAL_flexspi_nor_release))

# target_include_directories(${MCUX_SDK_PROJECT_NAME}} PRIVATE ${ProjDirPath}/.../../corel/armgcc/release)}

# endif()

Figure 20. Delete or comment line 54 through line 60

```

b. The path that include incbin.

c. The include for incbin.

```

include(dilver_soc_sic_MIMYKIII\o^cm\)

88

89

include(driver_pmu_1_MIMXRT1176_cm7)

90

91

#include(utility incbin MIMXRT1176 cm7)

92

93

include(driver_clock_MIMXRT1176_cm7)

94

95

include (driver_common_MIMXRT1176_cm7)

96

97

include (device_MIMXRT1176_CMSIS_MIMXRT1176_cm7)

Figure 22. Delete or comment line 91

```

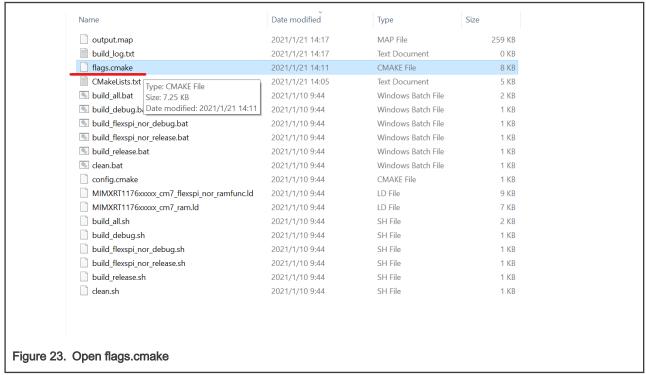

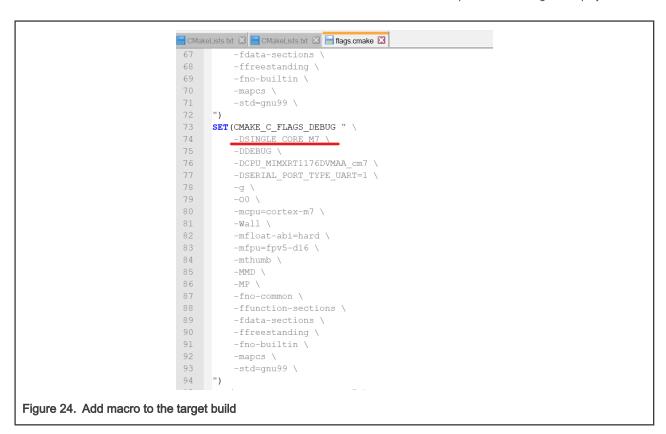

3. Open the file flags.cmake.

4. Add macro 'SINGLE\_CORE\_M7' to the target build.

13 / 17

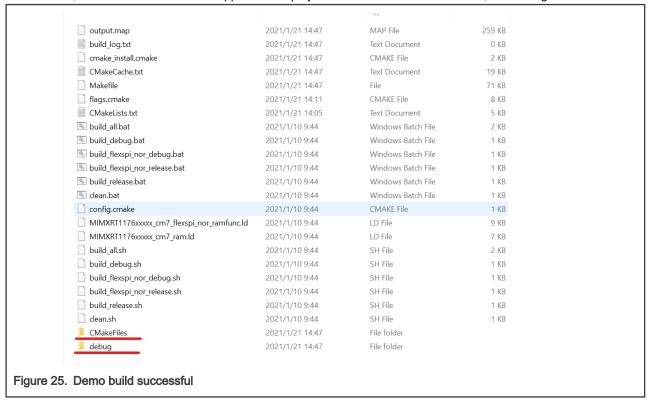

- 5. Save changes, double-click on build\_debug.bat to build the target.

- 6. If successful, there are two new folders appear in the project. The folders are: CmakeFiles, and debug.

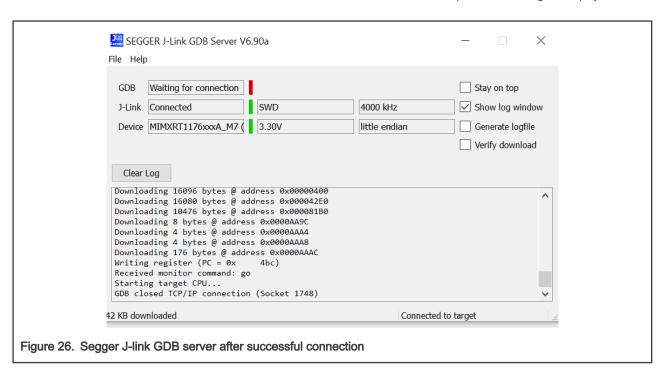

7. Open the J-Link GDB server application and connect to the device.

- 8. Open the GCC ARM Embedded tool chain command window.

- To launch the window, from the Windows operating system select, Start menu > GNU Tools ARM Embedded <version> > GCC Command Prompt.

10. Run the arm-none-eabi-gdb.exe <application\_name>.elf. The .elf file appears in the debug folder. For this example, it is arm-none-eabi-gdb.exe power\_mode\_switch\_bm\_core0.elf.

```

🚾 GCC Command Prompt - arm-none-eabi-gdb.exe C:\SDK_2.9.0_MIMXRT1170-EVK\boards\evkmimxrt1170\demo_apps\power_mode_switch\bm\core0...

:\Program Files (x86)\GNU Arm Embedded Toolchain\10 2020-q4-major>arm-none-eabi-gdb.exe C:\SDK_2.9.0_MIMXRT1170-EVK\boads\evkmimxrt1170\demo_apps\power_mode_switch\bm\core0\armgcc\debug\power_mode_switch_bm_core0.elf

:\Program Files (x86)\GNU Arm Embedded Toolchain\10 2020-q4-major\bin\arm-none-eabi-gdb.exe: warning: Couldn't determin a path for the index cache directory.

NV gdb (GNU Arm Embedded Toolchain 10-2020-q4-major) 10.1.90.20201028-git Copyright (C) 2020 Free Software Foundation, Inc. license GPLv3+: GNU GPL version 3 or later 'http://gnu.org/licenses/gpl.html> his is free software: you are free to change and redistribute it. There is NO WARRANTY, to the extent permitted by law. Type "show copying" and "show warranty" for details. This GDB was configured as "--host=i686-w64-mingw32 --target=arm-none-eabi". Type "show configuration" for configuration details. For bug reporting instructions, please see: https://www.gnu.org/software/gdb/bugs/>

Find the GDB manual and other documentation resources online at: (http://www.gnu.org/software/gdb/documentation/).

<a href="http://www.gnu.org/software/gdb/documentation/">http://www.gnu.org/software/gdb/documentation/</a>

or help, type "help".

ype "apropos word" to search for commands related to "word"...

eading symbols from C:\SDK_2.9.0_MIMXRT1170-EVK\boards\evkmimxrt1170\demo_apps\power_mode_switch\bm\core0\armgcc\debug

ower_mode_switch_bm_core0.elf...

gdh)

Figure 28. Run arm-none-eabi-gdb

```

- 11. Run the following commands:

- a. Target remote localhost: 2331

- b. Monitor reset

- c. Monitor halt

- d. Load

```

For help, type "help".

Type "apropos word" to search for commands related to "word"...

Reading symbols from C:\SDK_2.9.0_MIMXRT1170-EVK\boards\evkmimxrt1170\demo_apps\pow

(gdb) target remote localhost:2331

Remote debugging using localhost:2331

(gdb) monitor reset

Resetting target

(gdb) monitor halt

(gdb) <u>l</u>oad

Loading section .interrupts, size 0x400 lma 0x0

Loading section .text, size 0xa69c 1ma 0x400

Loading section .ARM, size 0x8 1ma 0xaa9c

Loading section .init_array, size 0x4 1ma 0xaaa4

Loading section .fini_array, size 0x4 lma 0xaaa8

Loading section .data, size 0xb0 lma 0xaaac

Start address 0x000004bc, load size 43868

Transfer rate: 96 KB/sec, 5483 bytes/write.

(gdb) _

Figure 29. Run the debug commands

```

12. Run the command **monitor go** to start the demo and the result appears on the terminal window.

How To Reach Us

Home Page:

nxp.com

Web Support:

nxp.com/support

Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/SalesTermsandConditions.

**Right to make changes** - NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Security — Customer understands that all NXP products may be subject to unidentified or documented vulnerabilities. Customer is responsible for the design and operation of its applications and products throughout their lifecycles to reduce the effect of these vulnerabilities on customer's applications and products. Customer's responsibility also extends to other open and/or proprietary technologies supported by NXP products for use in customer's applications. NXP accepts no liability for any vulnerability. Customer should regularly check security updates from NXP and follow up appropriately. Customer shall select products with security features that best meet rules, regulations, and standards of the intended application and make the ultimate design decisions regarding its products and is solely responsible for compliance with all legal, regulatory, and security related requirements concerning its products, regardless of any information or support that may be provided by NXP. NXP has a Product Security Incident Response Team (PSIRT) (reachable at PSIRT@nxp.com) that manages the investigation, reporting, and solution release to security vulnerabilities of NXP products.

NXP, the NXP logo, NXP SECURE CONNECTIONS FOR A SMARTER WORLD, COOLFLUX,EMBRACE, GREENCHIP, HITAG, ICODE, JCOP, LIFE, VIBES, MIFARE, MIFARE CLASSIC, MIFARE DESFire, MIFARE PLUS, MIFARE FLEX, MANTIS, MIFARE ULTRALIGHT, MIFARE4MOBILE, MIGLO, NTAG, ROADLINK, SMARTLX, SMARTMX, STARPLUG, TOPFET, TRENCHMOS, UCODE, Freescale, the Freescale logo, AltiVec, CodeWarrior, ColdFire, ColdFire+, the Energy Efficient Solutions logo, Kinetis, Layerscape, MagniV, mobileGT, PEG, PowerQUICC, Processor Expert, QorlQ, QorlQ Qonverge, SafeAssure, the SafeAssure logo, StarCore, Symphony, VortiQa, Vybrid, Airfast, BeeKit, BeeStack, CoreNet, Flexis, MXC, Platform in a Package, QUICC Engine, Tower, TurboLink, EdgeScale, EdgeLock, elQ, and Immersive3D are trademarks of NXP B.V. All other product or service names are the property of their respective owners. AMBA, Arm, Arm7, Arm7TDMI, Arm9, Arm11, Artisan, big.LITTLE, Cordio, CoreLink, CoreSight, Cortex, DesignStart, DynamIQ, Jazelle, Keil, Mali, Mbed, Mbed Enabled, NEON, POP, RealView, SecurCore, Socrates, Thumb, TrustZone, ULINK, ULINK2, ULINK-ME, ULINK-PLUS, ULINKpro, µVision, Versatile are trademarks or registered trademarks of Arm Limited (or its subsidiaries) in the US and/or elsewhere. The related technology may be protected by any or all of patents, copyrights, designs and trade secrets. All rights reserved. Oracle and Java are registered trademarks of Oracle and/or its affiliates. The Power Architecture and Power.org word marks and the Power and Power.org logos and related marks are trademarks and service marks licensed by Power.org.

© NXP B.V. 2021.

All rights reserved.

For more information, please visit: http://www.nxp.com

For sales office addresses, please send an email to: salesaddresses@nxp.com

Date of release: 02 February 2021

Document identifier: AN13116